DDR4简介

DRAM的存储原理

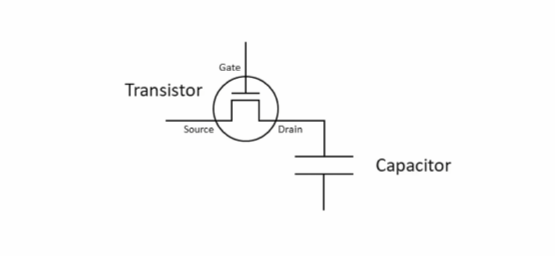

DRAM的基本存储单元:cell

一个cell由一个晶体管和一个电容(约为30pF)组成,电容存储了电量代表1,电容放空电量代表0,晶体管作为电容的充放电开关,以便实现1bit数据的读写,cell的结构如下图所示 :

读的过程:首先打开MOS管,根据电容的充放电信息获得存储bit。如果该cell存储值为“1”,即电容此时存有电荷,那么打开MOS管后,电容就会开始放电;如果cell为“0”,那么MOS管打开后,电容不会放电

写的过程:首先打开MOS管,在S极施加对应电压完成bit 1 和bit 0的写入。如果施加高电压,那么电流就会通过MOS管向电容充电;如果要写bit 0,则让S极接低电平。

保持过程:写入完成后,MOS管被关闭,由于MOS管断开后电阻极大,电容上的电荷几乎没有泄放路径。根据电路理论(Q = C * V,电荷量=电容 * 电压),只要没有放电路径,电荷就会保留在电容上,电容电压也就得以维持。

刷新的必要性:由于MOS管关闭时电阻极大,但未无穷大,cell中还存在着微小的泄漏电流,导致电容上的电荷缓慢流失,因此电容上的电压,也即是cell存储的数据无法永久保持,只能维持一段时间(通常是几十ms左右)。这就是被称为DRAM(Dynamic RAM)的原因——数据是动态的,会随着时间衰减,因此DRAM需要进行定期刷新操作,刷新操作是在cell的数据丢失之前,控制器会再次打开MOS管,Sense Amplifier(感应放大器)会读取电容上的电压(是高于还是低于阈值),然后将其刷新到原来的电平,从而将电容电荷恢复到满状态。

DRAM的刷新方式

这个过程后面详细补充。

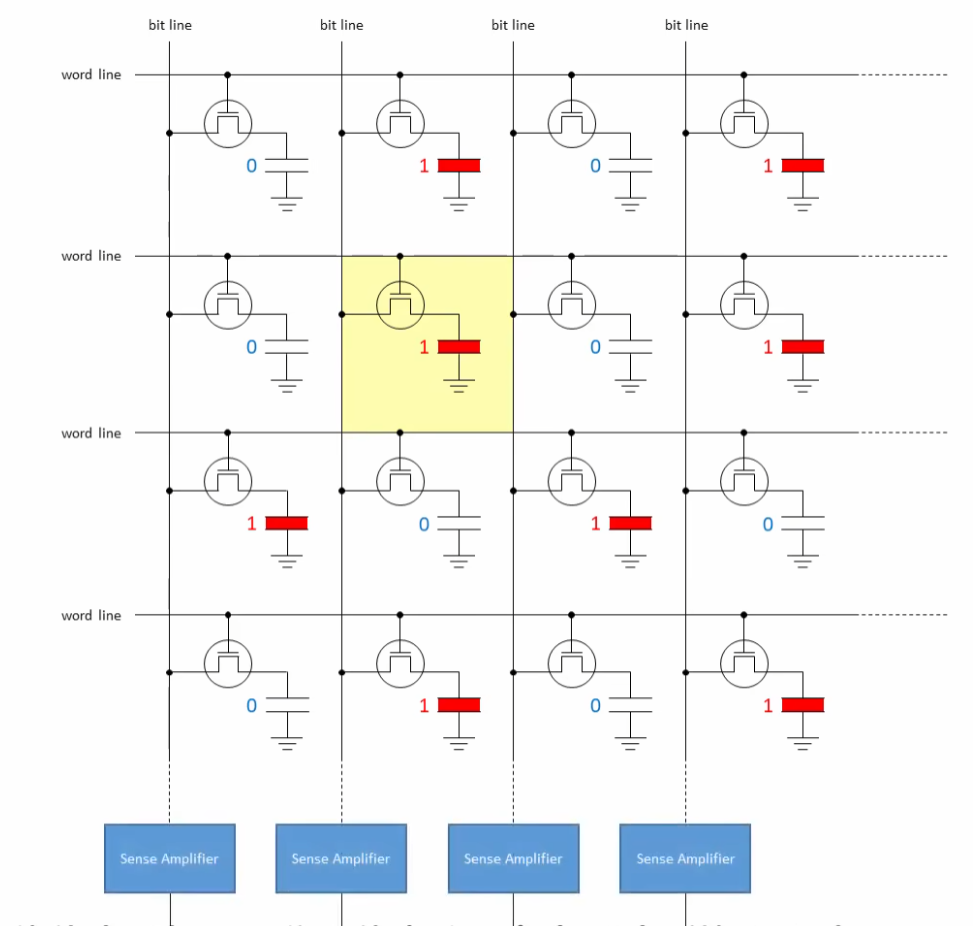

DRAM的二维存储阵列

在DRAM芯片中,存储单元呈二维阵列排布,接上了字线(word line,一个字是两个字节)和位线(bit line)。

假设在这个阵列中,有些单元存储了bit 1,有些存储了bit 0,假设我们需要读取出某个存储单元的值,这就需要在位线末端加入Sense Amplifier电路。

在DRAM的阵列中,每个Sense Amplifier连到了两个不同的位线上,Sense Amplifier就将DRAM存储单元划分了两片区域,这种叫做开放位线(Open Bitline)布局(也有别的方式)。

讲回上面的问题,如果要读取特定cell的数据,首先要读取一整行的cell

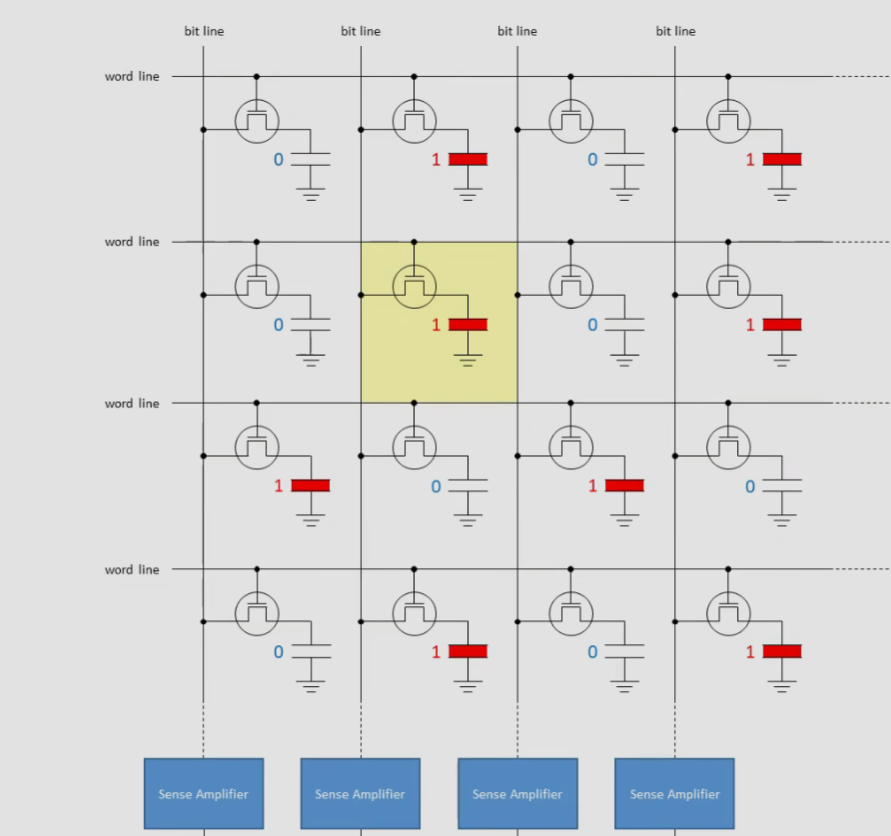

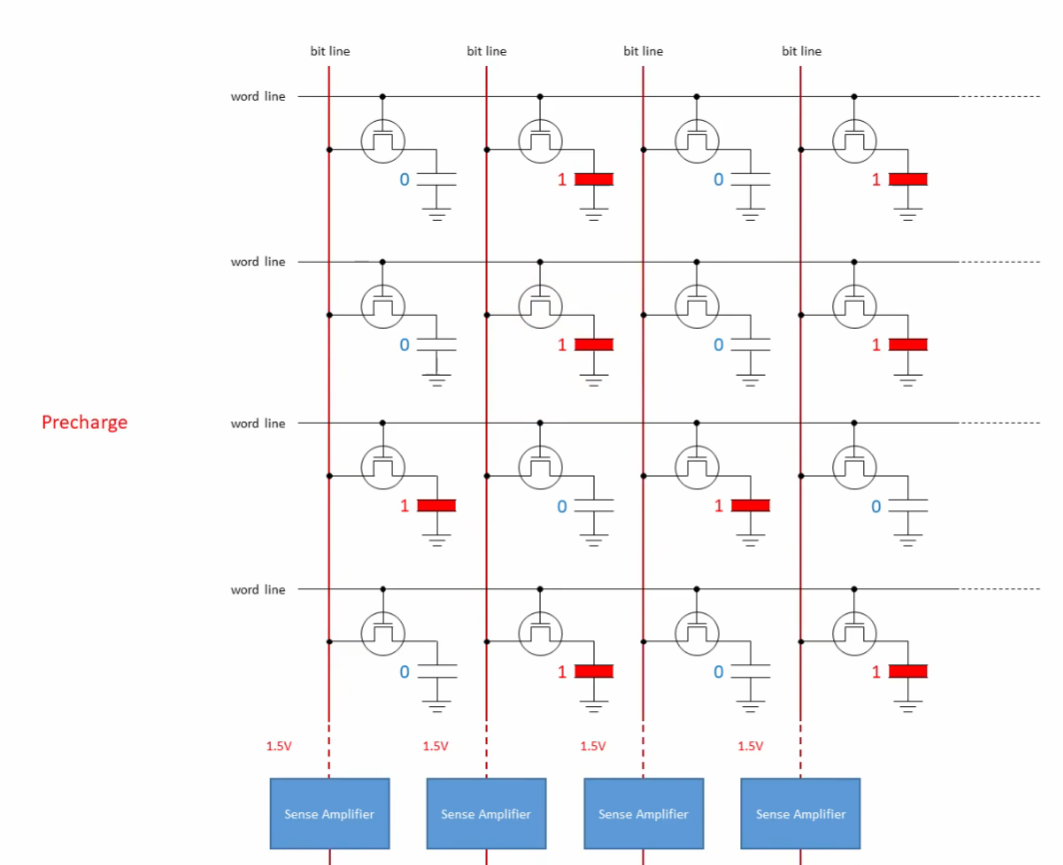

位线被Precharge(预加电)到DRAM供电电压的一半的电压,这个过程很短暂,然后将位线悬空,因此cell仍然处于充电的状态。

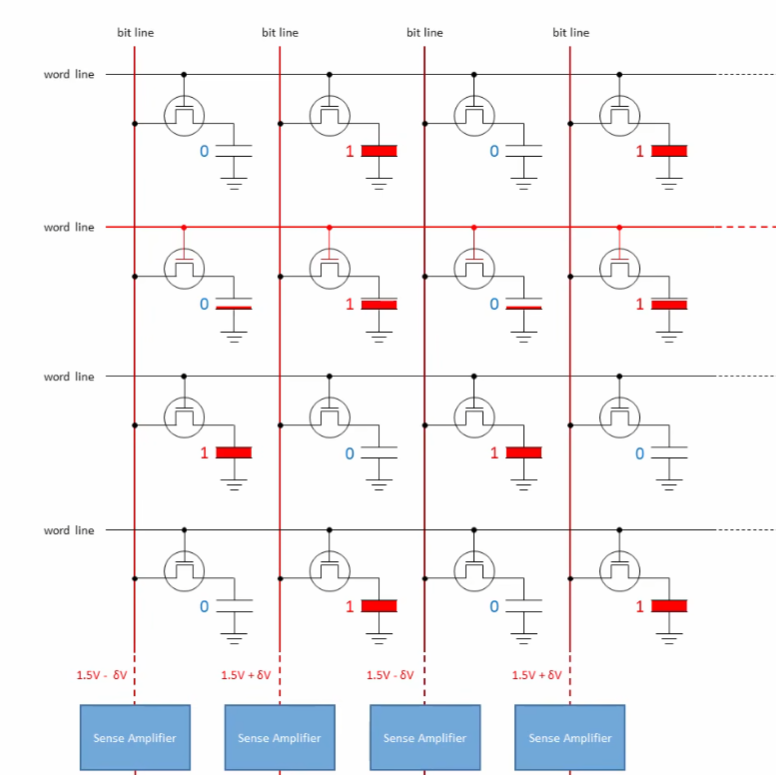

此时将要读取的cell所在的字线拉高至高电平,也成为置位,此时cell的MOS管将打开。如果电容器充满了电,电荷会从电容流向位线,电容放掉一点电,位线的电压就会抬升一些;如果电容没有电,电荷会从位线流向电容,电容充一点电,位线的电压就会降低一点。

±δ表示的位线上的电压变化只会发生几ns,电压变化也会只有几mV,这是因为位线上的的电容远大于cell的电容,但是这个电压变化已经足以让Sense Amplifier感受到了。Sense Amplifier把新电压与之前的电压做比较(此时Sense Amplifier另外一边的位线仍然处于1.5V,这也是为什么叫做差分Sense Amplifier的原因)。Sense Amplifier含有翻转器,锁存器等电路,可以用来临时存储刚刚读出来的值。

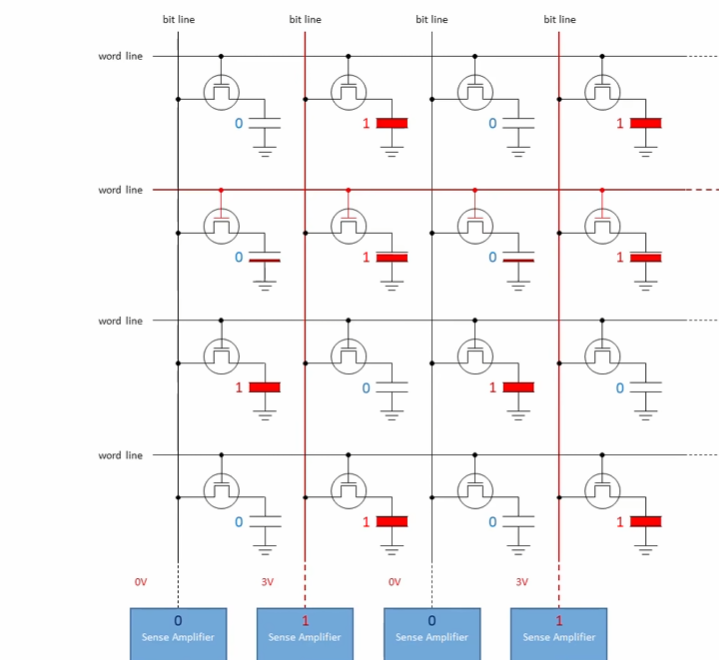

因此,读取DRAM一行的cell存储的数据是破坏性的,为了确定一个cell是否充了电,那个cell以及其他cell至少都会放一点电,这意味着,每次读操作过后,都要进行写操作,这也是Sense Amplifier的工作。根据锁存的值,这些位线有些被拉到DRAM的最高电压(3V),有些则被接地。实际上为了改变 一个cell的值,也是需要先读后写的。

https://www.bilibili.com/video/BV1T3411T73E?vd_source=02d778492044501f15e5a7887e756600&spm_id_from=333.788.videopod.episodes&p=2