二进制解码器

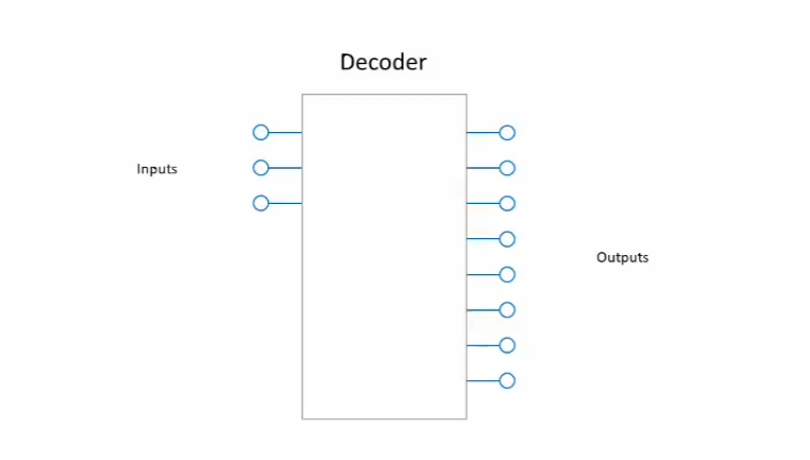

3比特的二进制解码器可以由下图表示。每种组合方式对应着解码器的不同输出。

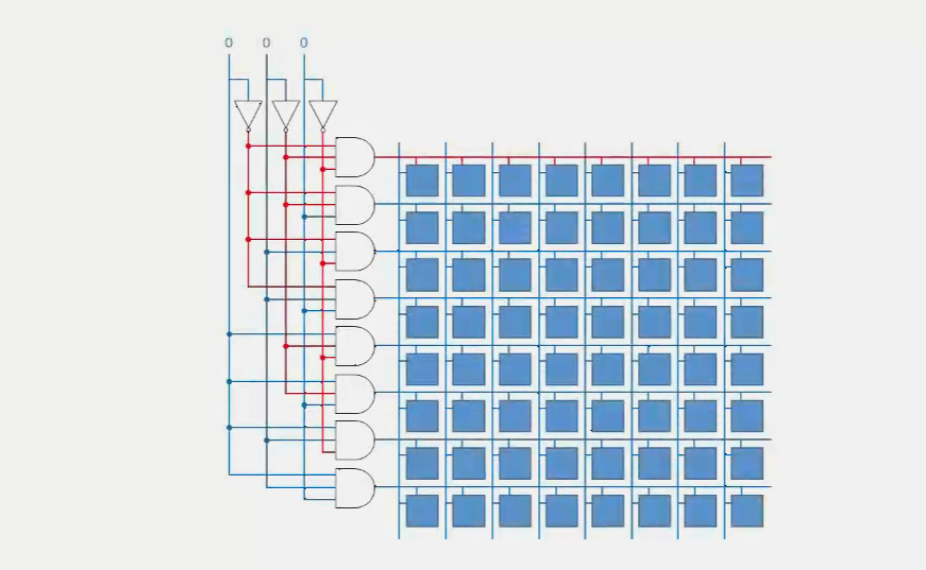

3-8解码器可以用三个非门和三个与门构成

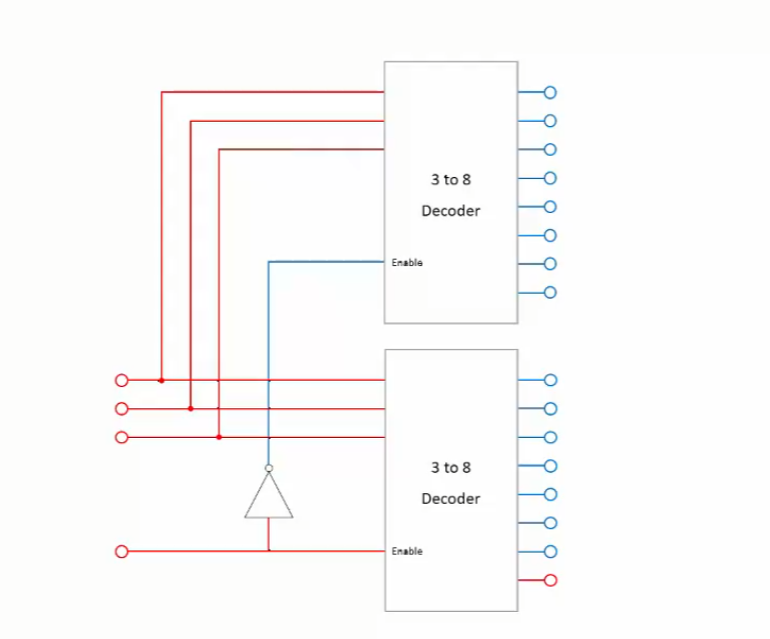

解码器可以拼接起来组成更大的解码器,比如两个3-8解码器可以拼起来组成一个4-16解码器。

选通器和分配器。

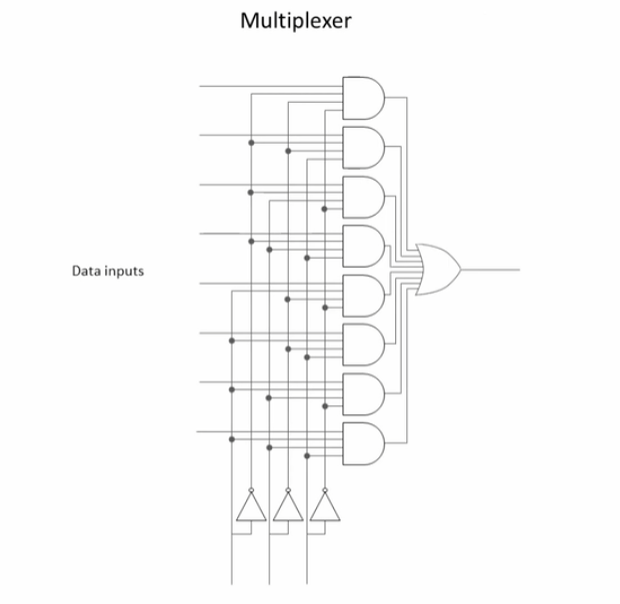

选通器

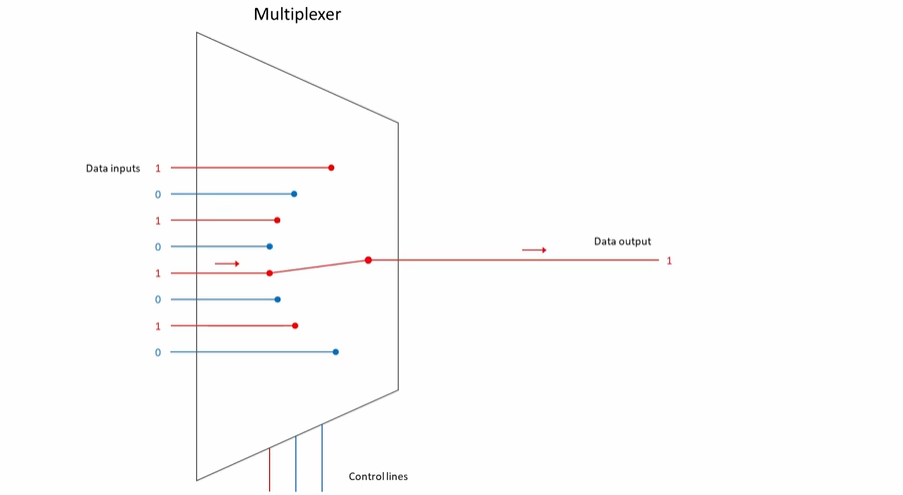

一个8选1的选通器如下图所示。本质上,选通器是在多个输入信号中,选择一个通到输出口的器件。选通器需要额外的输入,用来决定选哪个输入作为输出,这个信号名叫控制线,改变控制线的值,每个输入都能被输出口上。

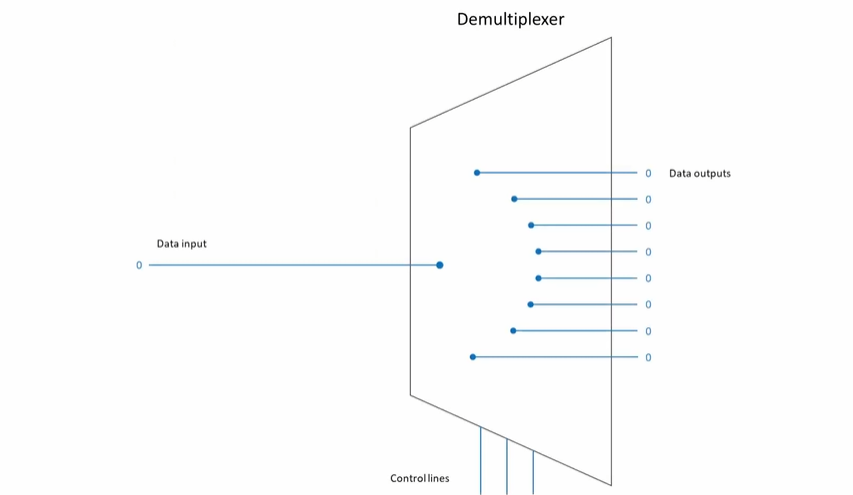

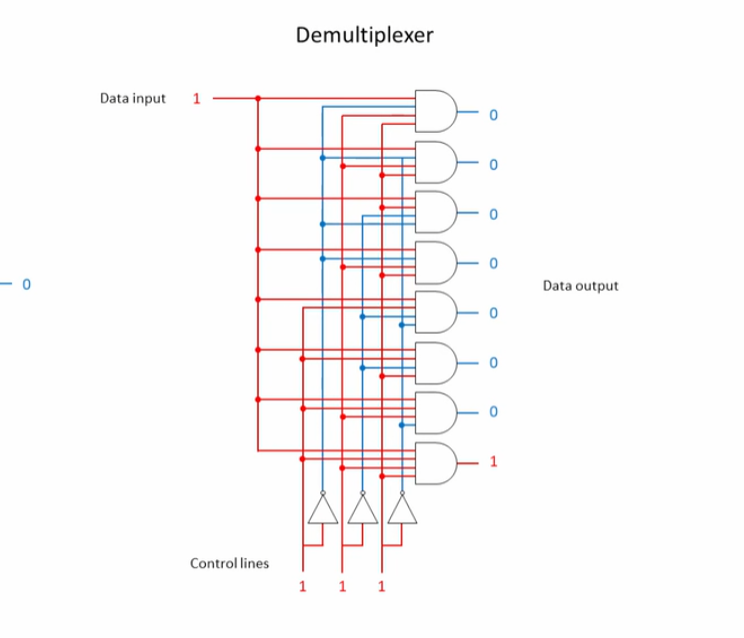

分配器

分配器功能与选通器相反,它将一个输入接通到多个输出中的一个上面,下面就是一个1转8分配器。根据控制线的值,一个输入会接通道其中一个输出上。

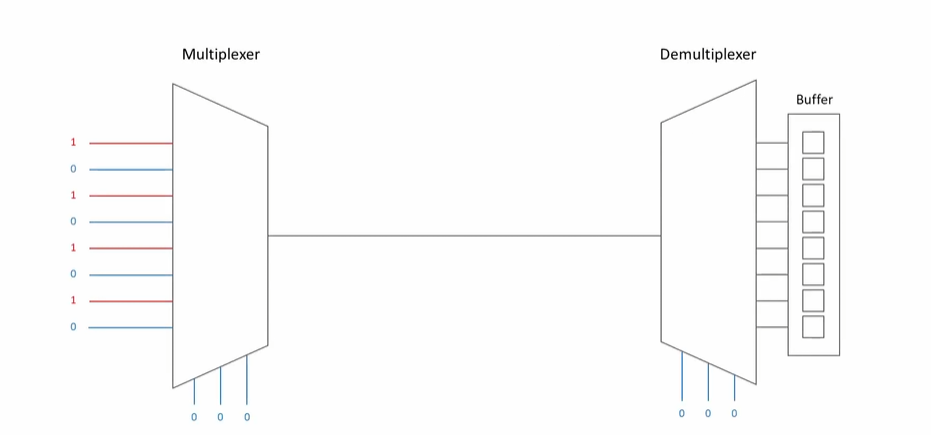

选通器和分配器经常一起使用,例如把并行数据转为串行数据,再复原。但是在数据重新组装的过程中,需要一组缓存把数据存下来,最后发送出去。

这是一个8选1的选通器,左边是8跟输入线,右边是1根输出线,底部是3根控制线。

这是一个1-8的分配器,其实跟带使能的解码器电路一模一样,使能口用作输入口。

在DRAM中,对于读操作,就是选通器把其中一个Sense Amplifier的值根据列地址选出来,然后放在输出口。对于写操作,就是分配器把输入值给某个Sense Amplifier更新其数据。而内存控制器上的一个选通器把地址分为行地址和列地址,再输出给DRAM。