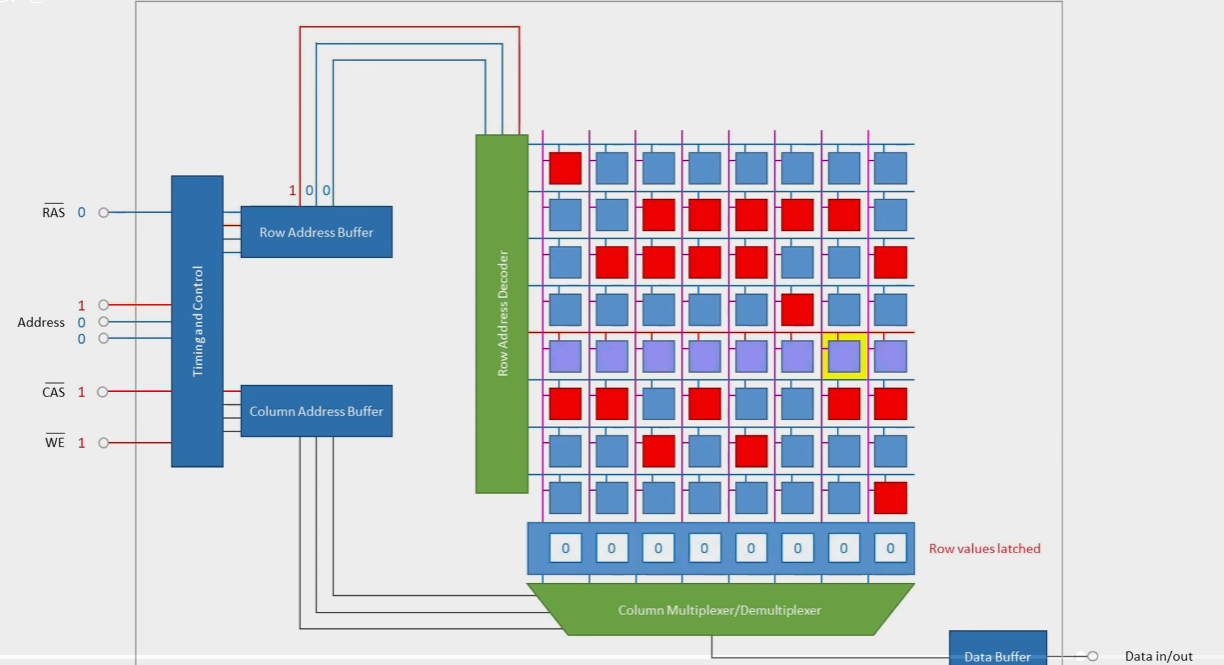

DRAM读写循环

以一个8 * 8 的二维阵列为例子,假设部分存储单元为1,部分为0,现在要读写其中某一个cell的值。

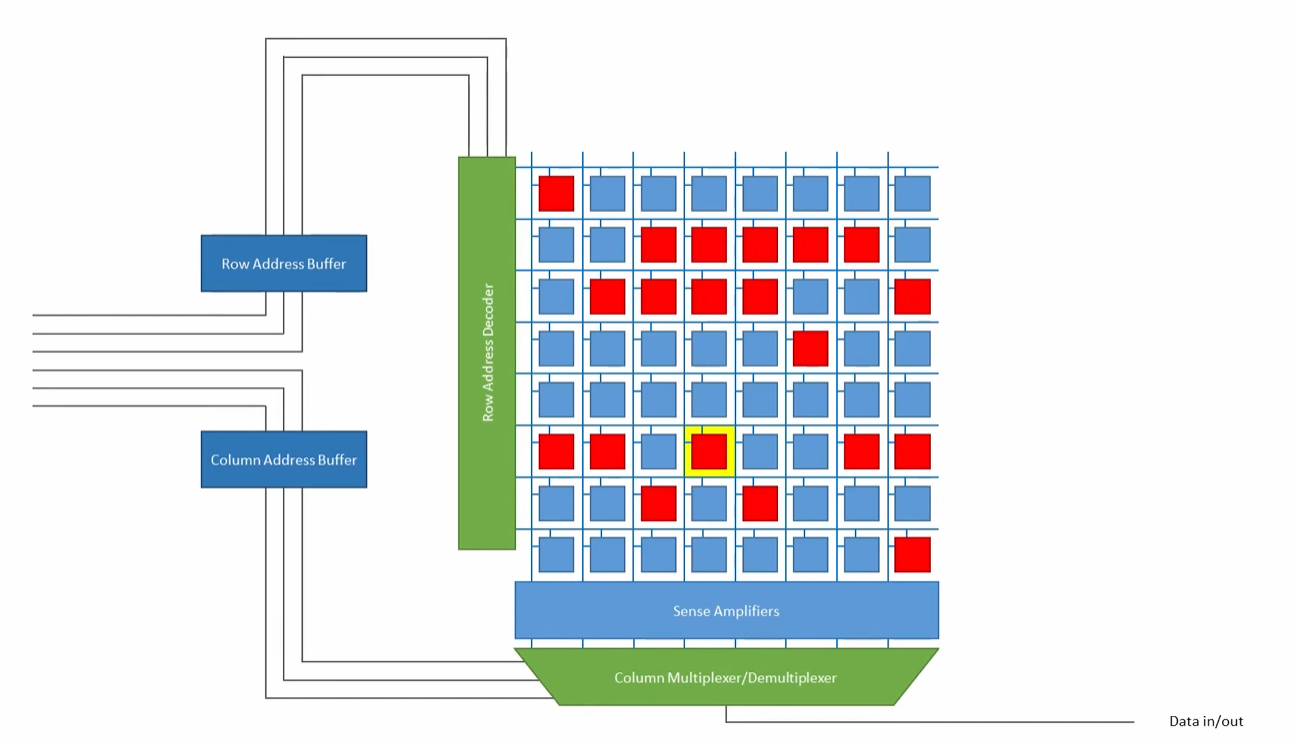

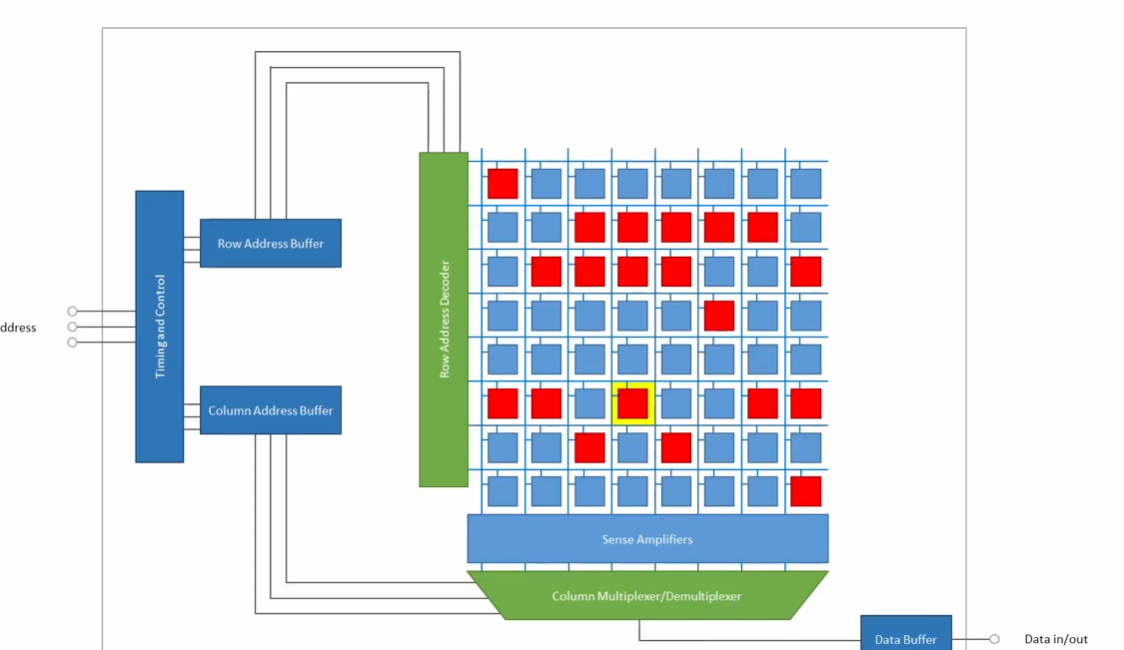

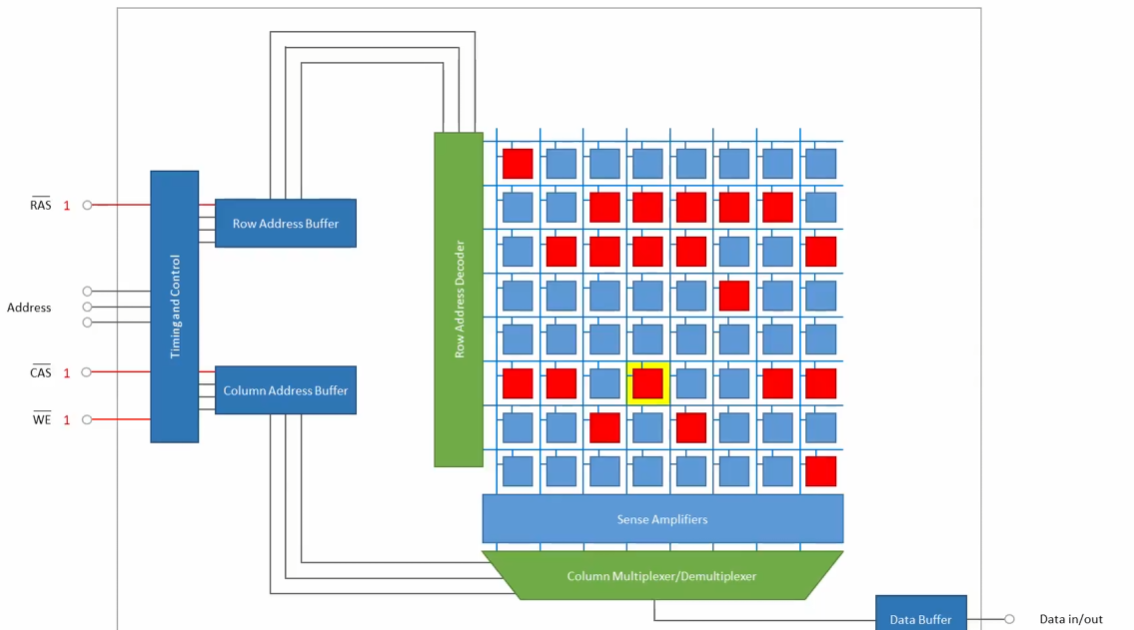

为了确定存储的位置,我们需要内存地址,为了传输内存地址,我们需要地址总线。8 * 8阵列一共有64个cell,我们需要6线地址总线,一共能表示64种二进制值。三根地址总线被一起送入一排锁存器,名为行地址缓存(Row Address Buffer),这些锁存器连接到行地址解码器(Row Address Decoder)。这三根线携带的值足以用于区分阵列中的任意一行,这个值也称为行地址。另外三根总线则是送入另外一排锁存器,名为列地址缓存(Column Address Buffer),然后连上列选通器(Multiplexer)/分配器(Demultiplexer),这三根线携带的值足以用于区分阵列中的任意一列,这个值也称为列地址。

行列地址锁存器的职责就是零食存储行地址和列地址。这些锁存器可以让行地址和列地址分开送入DRAM,并通过一个内存地址多路复用系统。由于上图只读写1bit数据,所以我们的数据引脚只有一根(右下角可见)。数据引脚是双向的,既可以读取也可以写入。而一个DRAM通常有很多的数据引脚。

除了地址数据,还有控制信号、电源引脚。比如,给地址的行,列地址缓存器各加一条线,在地址输入时候,它们就能够先后被使能。 这两根线叫做行地址选通脉冲(RAS)和列地址选通脉冲(CAS)。DRAM还有低电平有效的写使能引脚,来表示数据是输入还是输出DRAM。

读操作:

包含以下步骤:

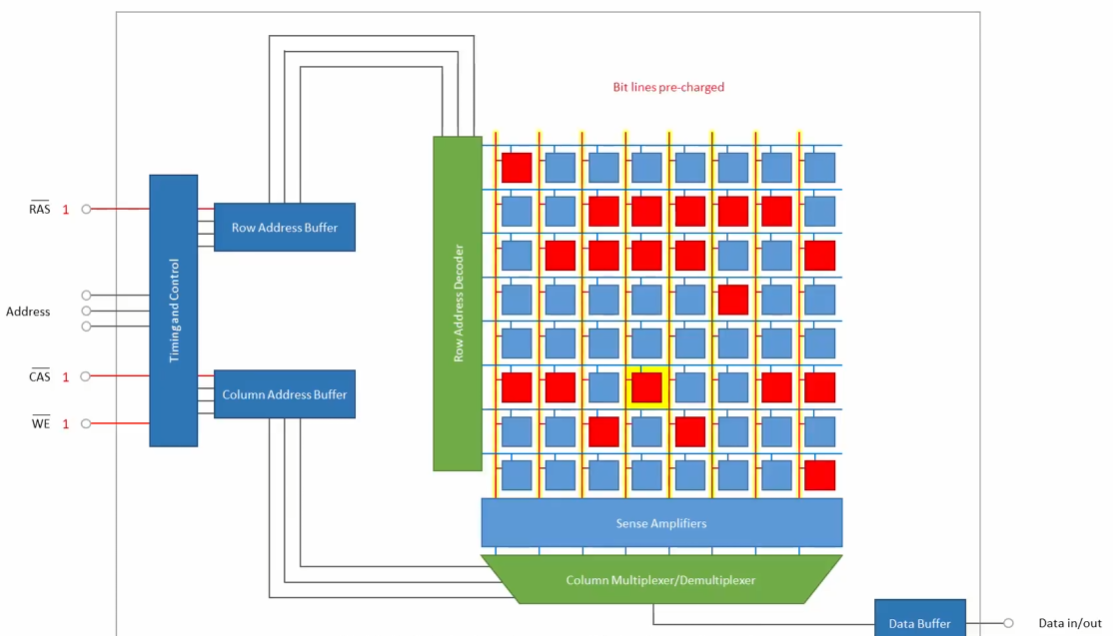

- 位线先被充电到DRAM供电电压的一半。

![image]()

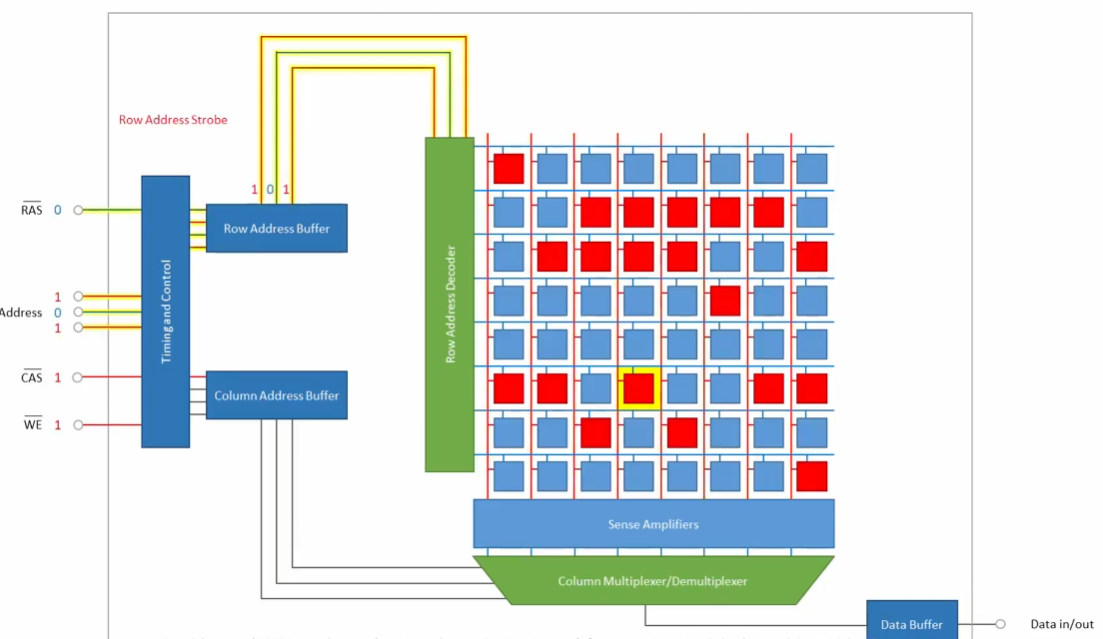

- 接着计算机的内存控制器将行地址输入到地址总线,并且使能RAS,与此同时,位线断开,处于悬空状态,行地址解码,读出来行地址。

![image]()

- 那一行的字线被置位,这一行的单元的值被锁存进Sense Amplifier,其中包含了我们需要读取的那个。

![image]()

- 含有1的cell会放部分电,含有0的cell会充部分电,但是原始数据已经被所存了。

- 列地址被放入地址总线,CAS也被使能,列地址别存入列地址缓存,列选通器件用列地址选出了其中一个Sense Amplifier的值

![image]()

- 选出来的数据直接送入数据缓存,RAS结束,,数据引脚上的输出有效。

- 最后,Sense Amplifier存储的数据刷新那一行。

- CAS结束,字线放开。数据引脚的数据不再有效。只有位线处于预充电状态,准备下次读取。

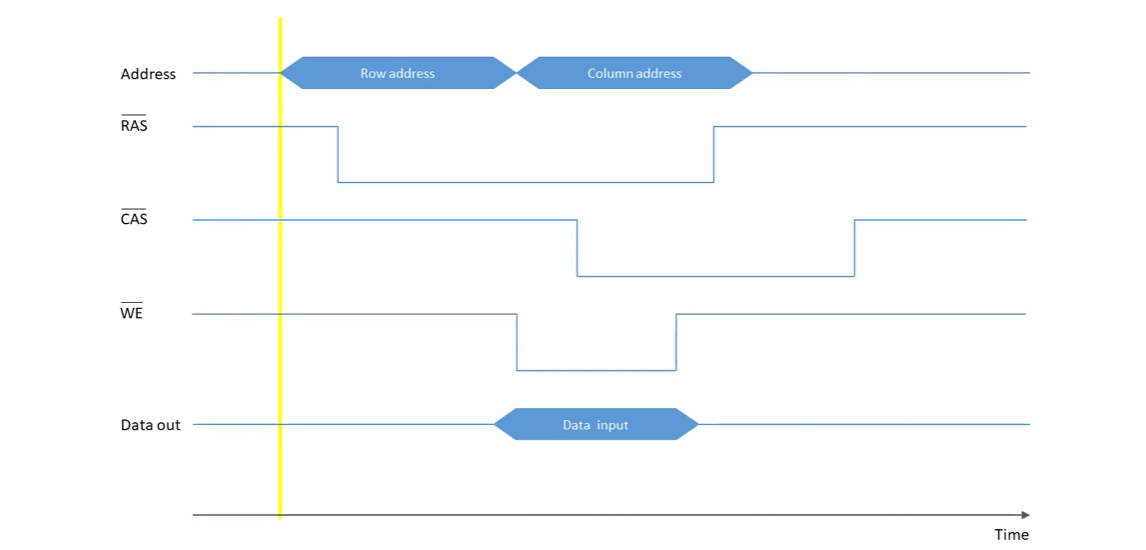

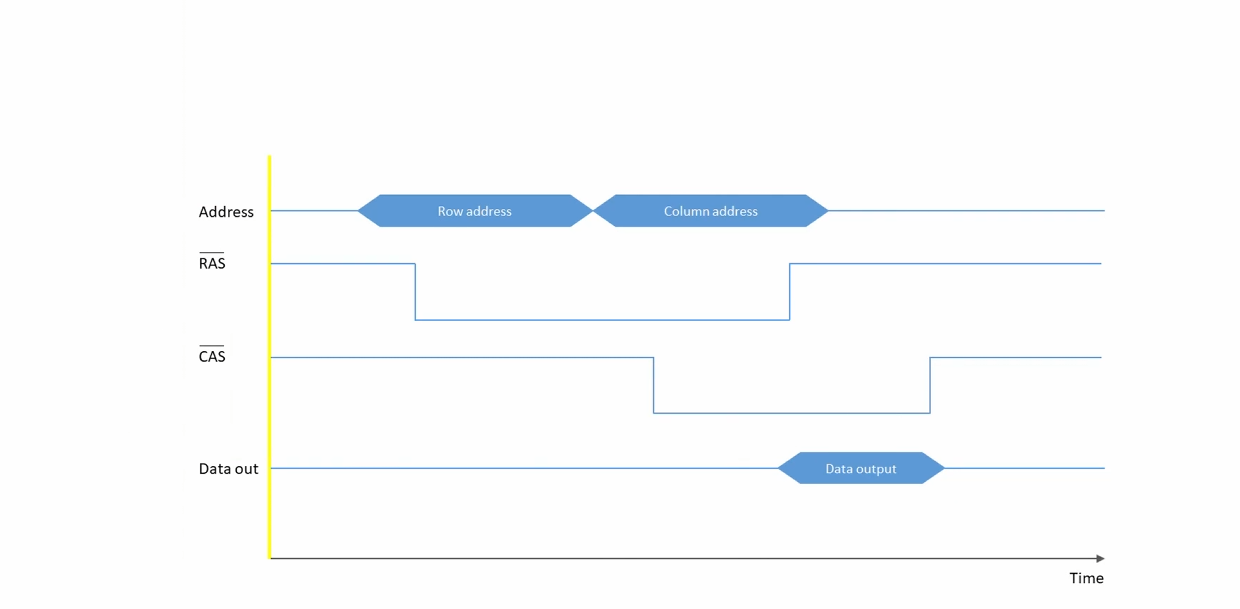

整个的时序过程:

写操作:

包含以下步骤:

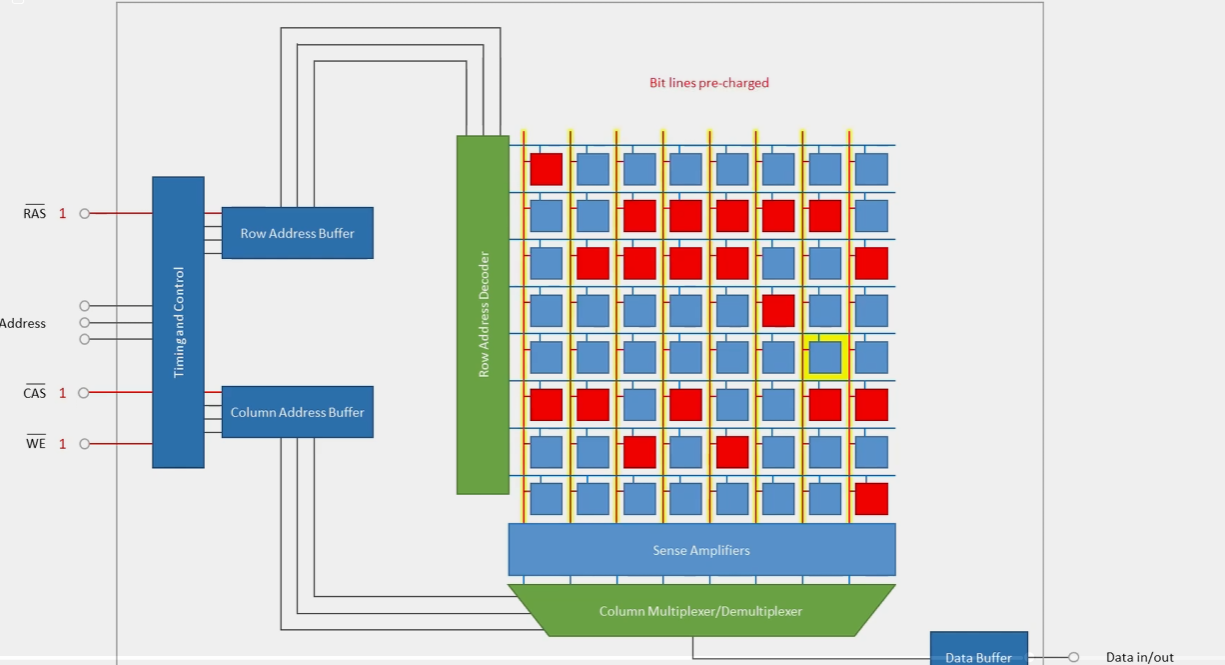

- 位线被预充电

![image]()

- 内存控制器输入正确的行地址,并且使能RAS,行地址被解码,与此同时,位线断开,处于悬空状态,行地址解码,读出来行地址。

![image]()

- 和读取一样,这一行的值会被所存进Sense Amplifier。

![image]()

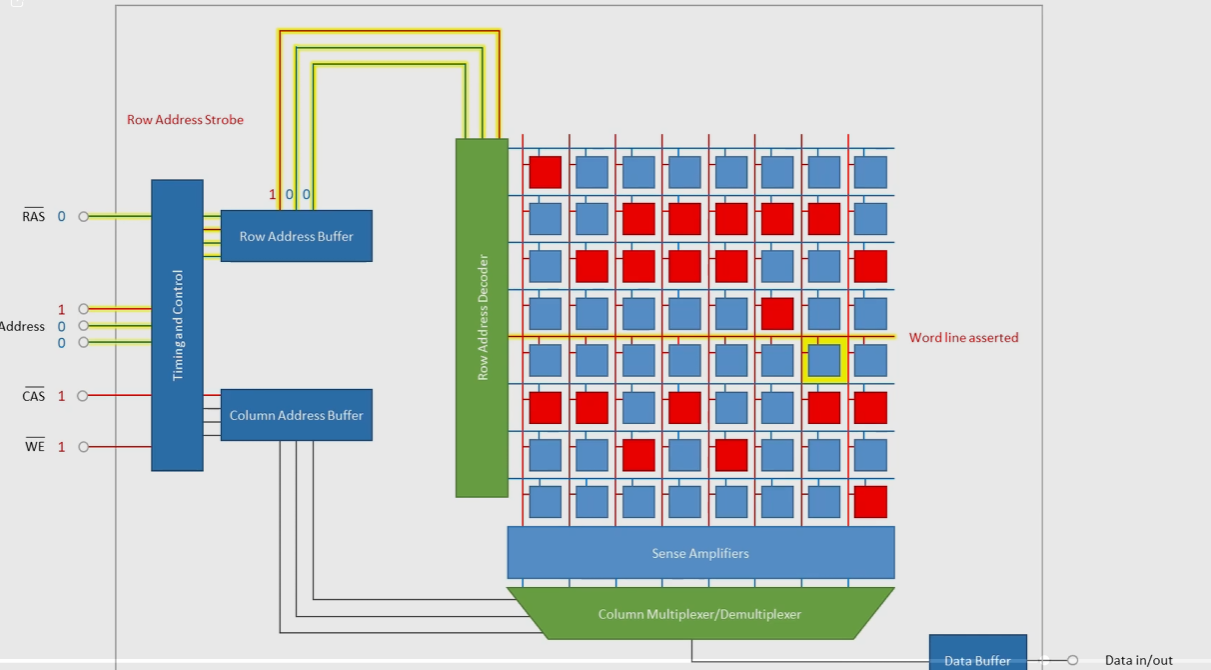

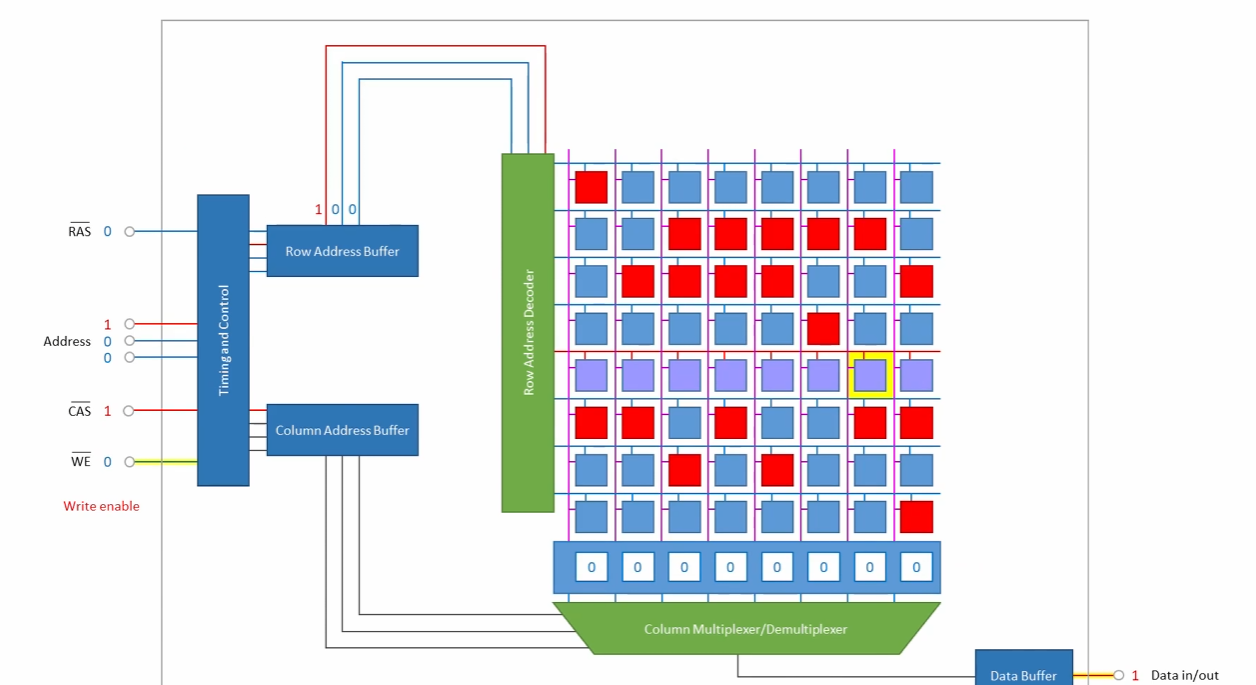

- 但是,在这个阶段,输入数据会被放在数据线上,WE信号也被使能。

![image]()

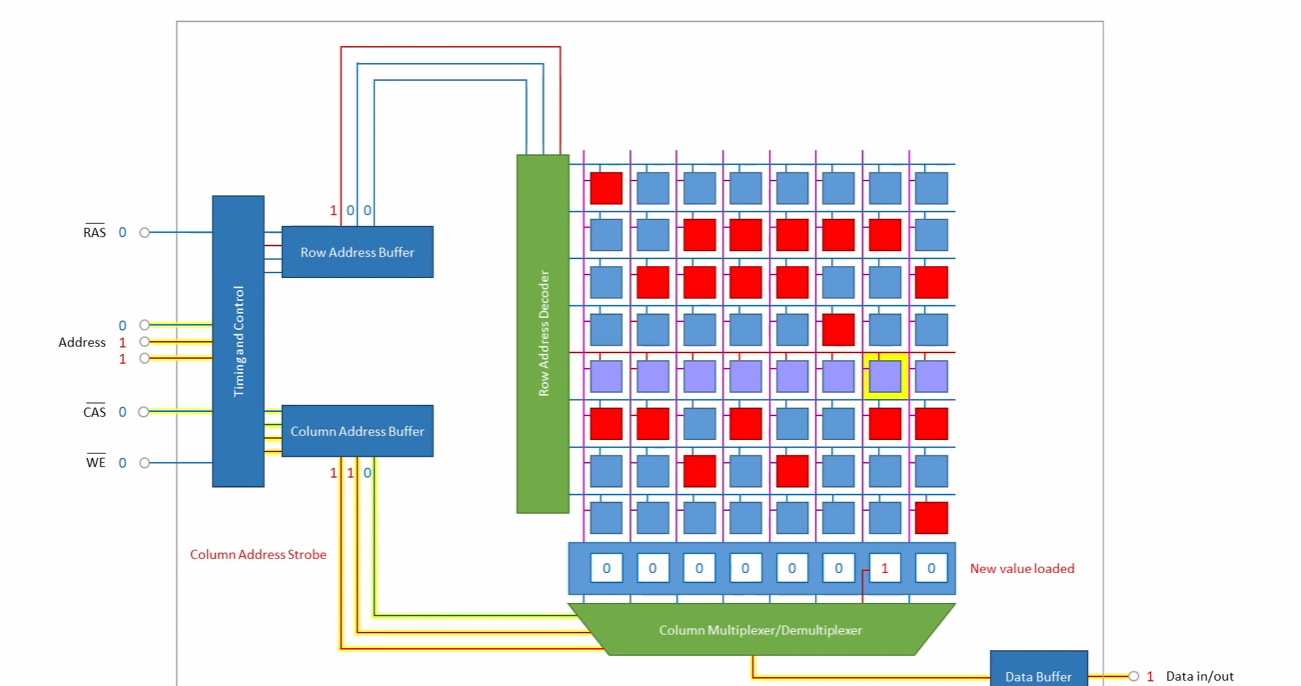

- 列分配器会把输入数据,根据列地址加载到对应的Sense Amplifier上

![image]()

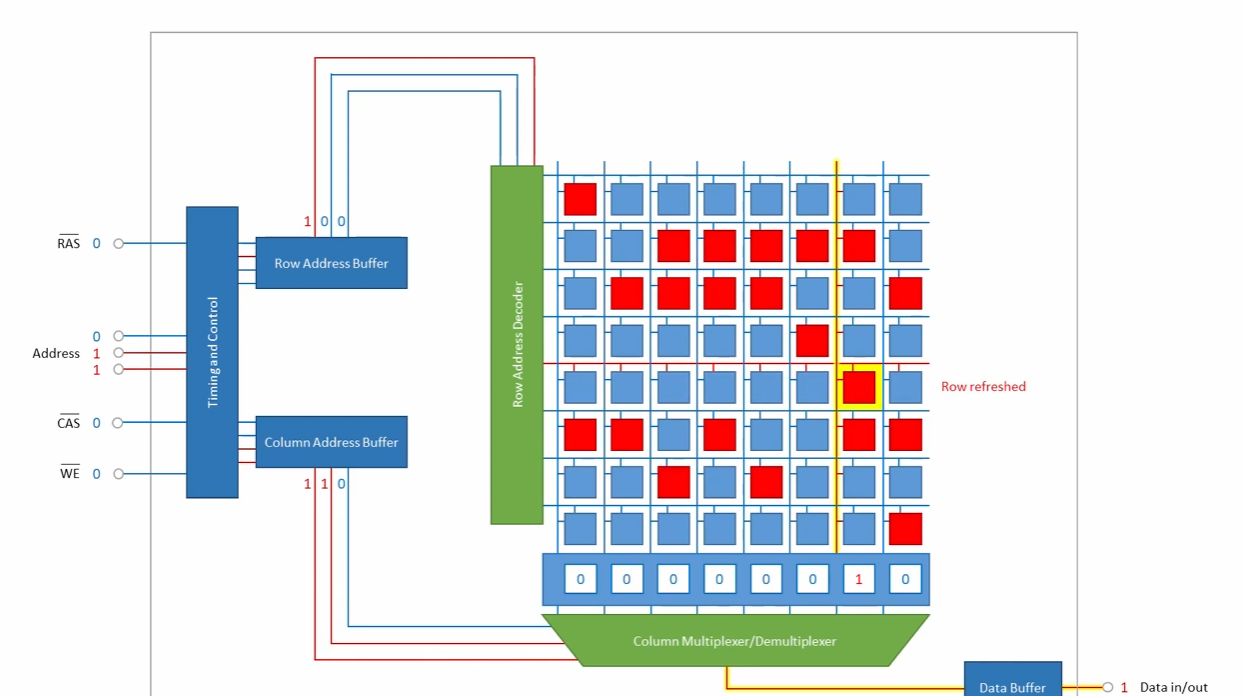

- 这一行同样被刷新,但是这次刷新用的是改过的数据。

![image]()

- WE信号结束,接着是RAS和CAS结束,位线重新被预充电。

整个的时序过程:

![image]()