Cache Maintenance registers and instructions

Armv8/v9 里定义的Cache的管理的操作有三种:

- Invalidate : 整个高速缓存或者某个高速缓存行。高速缓存上的数据会被丢弃。

- Clean : 整个高速缓存或者某个高速缓存行。相应的高速缓存行会被标记为脏,数据会写回到下一级高速缓存中或者主存储器中。

- Zero :在某些情况下,对高速缓存进行清零操作起到一个预取和加速的功效,比如当程序需要使用一大块临时内存,在初始化阶段对这个内存进行清零操作,这时高速缓存控制器会主动把这些零数据写入高速缓存行中。若程序主动使用高速缓存的清零操作,那么将大大减少系统内部总线的带宽。

既然谈到 cache 清零,那么我们就先看下和 cache 清零相关的寄存器和指令。

DCZID_EL0

在ARMv9架构中, DCZID_EL0 (Data Cache Zero ID Register)是一种系统寄存器,用于提供关于 “数据缓存清零 ”( DC GVA 和 DC GZVA )操作的信息。

DCZ操作是一种特殊的cache maintenance 指令,用于将缓存行中的数据设置为零。这种指令对于初始化或清理缓存内容非常有效,尤其是在需要快速清除大量数据以避免潜在的安全风险时。

DCZID_EL0寄存器字段解释

-

BS(Block Size)字段 :指示

DCZ操作可以影响的最小字节块大小。这个大小是2的幂次方,实际的块大小为 2 (BS+2) 字节。例如,如果BS字段的值为4,则DCZ操作影响的最小块大小为 2 (4+2) = 64 字节。 -

DZP(Data Zero Present)位 :这一位指示DCZ操作是否可用:

- 如果DZP位为0,则表示支持DCZ操作;

- 如果为1,则表示DCZ操作不可用。

这提供了一种检测硬件是否支持这种优化操作的方法。

DCZ 使用场景

DCZID_EL0 寄存器的信息对于操作系统和低级软件非常重要,它们需要了解和控制缓存行的具体行为。通过使用DCZ操作,软件可以有效地将缓存行初始化为零,这在多种场景下都非常有用,包括:

- 安全清理 :在释放敏感数据所占用的内存或缓存空间之前,确保数据被彻底清除,防止数据残留或泄露。

- 性能优化 :在某些应用场景中,预先清零缓存行可能会帮助提升程序的执行效率或减少延迟。

- 系统初始化 :在系统启动或任务启动时,快速初始化大量的内存或缓存区域,为后续操作准备干净的环境。

Cache maintenance 范围选择

对高速缓存的操作可以指定不同的范围。

- 整块高速缓存。

- 某个虚拟地址。

- 特定的高速缓存行或者组和路。

另外在ARMv8架构中最多可以支持7级的高速缓存,L1~L7高速缓存。当对一个高速缓存行进行操作时,我们需要知道高速缓存操作的范围。 具体如何选择操作哪一级cache 见文章 :【ARM Cache 及 MMU 系列文章 6 -- Cache 寄存器 CTR_EL0 CLIDR CCSIDR CSSELR 使用详解 1】

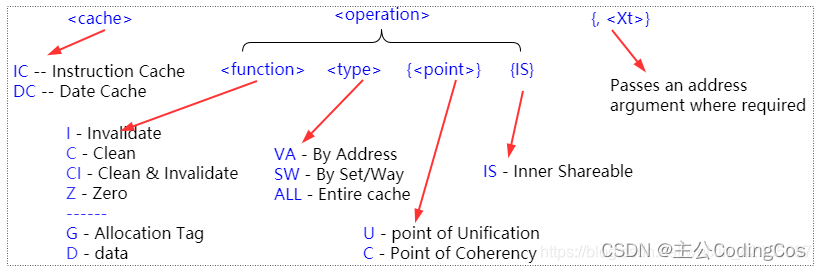

Cache maintenance 指令集

例如 :

DC IGDVAC:操作d-cache,根据虚拟地址无效掉data和Allocation Tags,操作范围到PoC;DC IGVAC:操作d-cache,根据虚拟地址无效掉Allocation Tags,操作范围到PoC。

关于PoC 和 PoU 的详细内容见 : 【ARM Cache 与 MMU 系列文章 2 -- Cache Coherence及内存顺序模学习】

最后,我们再看armv8文档中定义的cache指令集:

DC CISW, Data or unified Cache line Clean and Invalidate by Set/Way

DC CSW, Data or unified Cache line Clean by Set/Way

DC CVAU, Data or unified Cache line Clean by VA to PoU

DC ZVA, Data Cache Zero by VAIC IALLU, Instruction Cache Invalidate All to PoU

IC IALLU{, <Xt>}

IC IALLUIS, Instruction Cache Invalidate All to PoU, Inner Shareable

IC IALLUIS{, <Xt>}

IC IVAU, Instruction Cache line Invalidate by VA to PoU

IC IVAU{, <Xt>}DC CIVAC, Data or unified Cache line Clean and Invalidate by VA to PoC

DC CVAC, Data or unified Cache line Clean by VA to PoC

DC CVAP, Data or unified Cache line Clean by VA to PoP

DC GVA, Data Cache set Allocation Tag by VA

DC GZVA, Data Cache set Allocation Tags and Zero by VA

DC IGDSW, Data, Allocation Tag or unified Cache line Invalidate of Data and Allocation Tags by Set/Way

DC IGDVAC, Data, Allocation Tag or unified Cache line Invalidate of Allocation Tags by VA to PoC

DC IGSW, Data, Allocation Tag or unified Cache line Invalidate of Allocation Tags by Set/Way

DC IGVAC, Data, Allocation Tag or unified Cache line Invalidate of Allocation Tags by VA to PoC

DC ISW, Data or unified Cache line Invalidate by Set/Way

DC IVAC, Data or unified Cache line Invalidate by VA to PoC

DC CVADP, Data or unified Cache line Clean by VA to PoDPARMv8.5-MemTag:

DC CGDSW, Data, Allocation Tag or unified Cache line Clean of Data and Allocation Tags by Set/Way

DC CGDVAC, Data, Allocation Tag or unified Cache line Clean of Allocation Tags by VA to PoC

DC CGDVADP, Data, Allocation Tag or unified Cache line Clean of Allocation Tags by VA to PoDP

DC CGDVAP, Data, Allocation Tag or unified Cache line Clean of Data and Allocation Tags by VA to PoP

DC CGSW, Data, Allocation Tag or unified Cache line Clean of Allocation Tags by Set/Way

DC CGVAC, Data, Allocation Tag or unified Cache line Clean of Allocation Tags by VA to PoC

DC CGVADP, Data, Allocation Tag or unified Cache line Clean of Data and Allocation Tags by VA to PoDP

DC CGVAP, Data, Allocation Tag or unified Cache line Clean of Allocation Tags by VA to PoP

DC CIGDSW, Data, Allocation Tag or unified Cache line Clean and Invalidate of Data and Allocation Tags by Set/Way

DC CIGDVAC, Data, Allocation Tag or unified Cache line Clean and Invalidate of Data and Allocation Tags by VA to PoC

DC CIGSW, Data, Allocation Tag or unified Cache line Clean and Invalidate of Allocation Tags by Set/Way

DC CIGVAC, Data, Allocation Tag or unified Cache line Clean and Invalidate of Allocation Tags by VA to PoC